意法半导体(STMicroelectronics)近年致力研发全空乏绝缘上覆矽(FD-SOI)技术,尽管鳍式场效电晶体(FinFET)在半导体产业获得较多注意。不过以技术与经济层面而言,FD-SOI仍有许多优势,包括临界电压(VT)选择、标准元件最佳化等等。

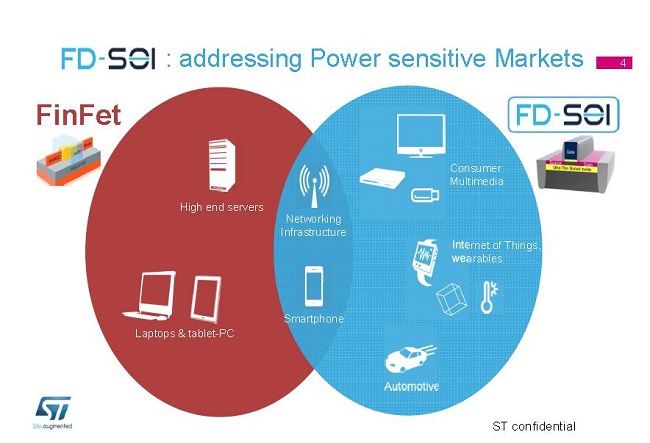

根据SemiWiki网站报导,目前28纳米FD-SOI制程节点虽然不是最新的制程节点,却是物联网(IoT)、汽车、消费性电子、移动等新兴市场最物超所值的芯片方案。

意法半导体为了推广FD-SOI技术,也将旗下28纳米FD-SOI技术策略性授权给三星电子(Samsung Electronics)、GlobalFoundries等晶圆大厂。三星在2014年中与意法半导体签署28纳米FD-SOI授权合作产制协议。

FD-SOI技术可控制电晶体的有效通道长度(effective channel length),漏电流也透过多偏置(poly-biasing)大幅减低,没有任何接面漏电(junction leakage)问题。

28纳米FD-SOI技术也提供0.6~1.1伏特操作电压,效能与功耗之间有更大取舍空间,其中特制多种临界电压元件库(multi-threshold-voltage libraries)包括普通临界电压以及低临界电压等选择。

而主要EDA/IP大厂也纷纷在设计流程和IP当中支援FD-SOI技术。2014年益华电脑(Cadence)宣布提供28纳米FD-SOI技术的IP解决方案。而2015年Synopsys宣布自家Lynx Design System开始支援FD-SOI技术。明导国际(Mentor)也在工具与设计流程支援FD-SOI制程。

FD-SOI技术最强大的一项机制是基底偏压(body-biasing),利用极薄的埋氧化层(buried oxide)控制电晶体通道,进一步强化效能或降低功耗。此外,在制程补偿(process compensation)过程中,基底偏压有助提升效能却不造成动态功率(dynamic Power)消耗。

FD-SOI技术属于平面型电晶体,制程简单、成本较低,无须通道掺杂(channel doping)处理,制程变异(process variation)也不如FinFET技术来得高,其光罩层与浸润式微影(immersion lithography)层数也比FinFET技术来得少。

意法半导体以FD-SOI技术为基础的标准元件库(standard cell library)专为主流、低功耗、高效能应用而最佳化,且有多样化选择,包括可程式化光罩ECO元件,亦有12轨高效能、8轨高密度架构供选择,将功耗、性能和面积(Power、Performance、Area;PPA)最佳化。

FD-SOI技术提供广泛的正反器(Flip Flop)选择,让系统设计师取舍空间更大。另外,也有创新的多位元正反器,可减少时脉树(clock-tree)流量,进而减少整体动态功率。此外,多位元正反器之间时钟变频器的分享行为,也致使漏电流减少。多阶段同步器则可减低多重时钟域电路内的亚稳态(metastability)效应。

这些SoC技术由标准元件主导,因为标准元件占据电晶体超过一半的面积,占4分之3的总电力消耗,也占据芯片4分之3的重要路径。因此,标准元件进行PPA最佳化的步骤相当重要,是SoC最佳化的关键。

FD-SOI技术目前处于技术优势,因为可区隔不同的PPA因应不同市场需求。举例而言,超低功耗、超低漏电流元件库可运用于物联网与穿戴式装置,而低功耗、低成本元件库则可应用于射频(RF)类比传输系统,像是智能型手机、网路应用等等。

最后,业者预计将FD-SOI技术微缩至20纳米,甚至是14纳米,以达到低功耗、低成本的FinFET等级效能。GlobalFoundries发表自家22纳米FD-SOI技术“22FDX”平台,在不久的将来,也可望看到更多该领域的进展。