关键词:芯片嵌入;多层板芯片嵌入;基于型板组装;TSV;SiP

摘要:智能移动装置的高速发展正在驱动更先进芯片封装技术的开发,以满足多功能集成和小型化的要求。传统的解决方案,如多芯片模块,可能无法同时满足高密度和小型化需求。而先进的2.5D 硅基板TSV解决方案成本太高,特别是,在对成本敏感的消费类市场中不能使用。在这两者之间,芯片嵌入式封装可能是一个理想的解决方案,它不但有较高互联密度,较小封装尺寸,也可以实现多芯片集成。本文着重讨论了主动芯片的嵌入技术:二维扇出封装和三维封装叠加。二维结构包括扇出晶圆级封装和多层板中芯片嵌入,前者基于晶圆形式,后者基于型板形式。不同流程的选择造成成本和成品率的差异,也造成芯片放置时间的先后。本文讨论了“Die-First”、“Die-Mid”和“Die-Last”流程的优劣势。主动(有源)芯片嵌入的三维叠加有着与二维芯片嵌入类似的优势,只是主动芯片嵌入封装体的上端可以另外叠加封装体,以实现真正的SiP结构。本文还讨论了芯片嵌入技术的发展、未来增长、可能的封装形式和将来的路线图。

Embedded Die Packaging Technologies Enable Innovative 2D and 3D Structures for Portable Applications

Ron Huemoeller, Corey Reichman, Curtis Zwenger

(Amkor Technology, Inc.1900 South Price Road, Chandler, AZ 85286, USA)

Abstract: The dramatic growth in“smart”portable electronics is driving the need for a more sophisticated IC packaging approach that allows room for increasing functionality while meeting ever decreasing form factor requirements. Traditional solutions like Multi-Chip Modules (MCM) may not meet the intense I/O requirements and form factor restrictions concurrently. On the other hand, advanced solutions like 2.5D TSV silicon interposer may prove to be cost prohibitive, especially for applications serving cost-sensitive consumer markets. In the middle, however, embedded die packaging may strike the ideal combination with an increased I/O density, reduced footprint, and multi-die capability within a single IC package.

Embedded die packaging itself is diverse and can be configured in a variety of architectures. Passive device embedding is discussed, but the paper focuses primarily on active die embedding. Active die embedding has two general constructions: either as a 2D fan-out package or a 3D stacked package for higher levels of system integration. The 2D formats include platforms such as Fan Out Wafer Level packaging (FO-WLP) and embedded die in laminate. One of the primary differences in the 2

D structures is the processing format, the former on wafer and the latter on laminate panel. The choice between processing formats can have a significant impact on both cost and yield. The other difference between 2D formats is the timing of the die placement in the process flow. The benefits and disadvantages of “Die First”, “Die Last” and “Die Mid” placement are discussed. The other active embedded die format is the 3D stacked package format with a modular System in Package (SiP)approach. 3D formats have similar distinctions as 2D formats, only with the added element of stacking one or more packages for a true SiP architecture. This paper also covers the evolution of embedded die, along with its projected growth, packaging formats and future roadmaps

Key Words: Embedded die; Embedded die in laminate; Panel-based assembly; SiP; TSV

一、简介

为应对小型化和高集成度的要求,模块化已成为半导体工业的关键,并由此产生众多封装方式。在较低端的技术方面,已经成熟的封装技术被广泛应用,如多芯片模块(MCM)就是利用了传统的基于标准和先进有机基板上的多芯片组合方法。在最高端的技术方面,最为先进的2.5D穿硅孔(TSV)技术平台利用带金属过孔的硅基板提供了高密度集成,却以高成本为代价。在这两者之间,芯片嵌入式(Embedded Die)平台也许提供了最具竞争力的优势,特别是从移动应用的角度审视。芯片嵌入式平台在之前所提到的两种技术平台之间有自己非常清晰的技术路径。芯片嵌入式平台为实现真正的系统型封装(SiP)提供了机会。它比现有的多芯片模块(MCM)具有更高的集成度,而比2.5D TSV 平台更具价格优势。

同时可以增加互联密度,减小封装体尺寸,和实施多芯片组合的能力使芯片嵌入式封装成为极具诱惑的解决方案。此外,芯片嵌入式产品将不同类型的芯片集成在同一个封装中,不仅可以利用标准JEDEC互联方式与其上部或下部的存储芯片相连,也可以与其它非标准的存储芯片相连。因此,为应对更高的系统集成要求,这个创新的时代将更多的芯片和系统功能转移到封装领域里,而芯片嵌入式封装的实施也成为有效满足技术路线图众多集成要求的关键技术。

二、 芯片嵌入式技术的演变

芯片嵌入式的定义是将一颗被动(无源)元件或一颗集成电路芯片植入有机线路板的内层或植入模块或芯片封装内部,使其看起来就像埋入完成的结构中,而不是置于其结构的上部或下部。图1是一个芯片嵌入式模块的例子。主动芯片嵌入式的优势包括小型化、电热性能提高、异质芯片集成、可能的成本降低和对原始设备制造商(OEM)来说更简单的供应链管理。

芯片嵌入式技术已经存在多年。被动元件如去耦电容常常被嵌入多层基板中。这些嵌入的去耦元件在线路板电源和地平面之间提供电容以减少高速数字电路封装中的切换噪声。虽然没有被动芯片嵌入那样普遍,主动芯片嵌入正快速成长。这是因为嵌入技术的提高、更好的成品率、同时,半导体工业的发展对异质芯片的集成有了更多的要求。主动芯片嵌入的例子包括扇出型晶圆级封装(FO-WLP),如飞思卡尔(Freescale)的重分布芯片封装(RCP)和英飞凌(Infineon)的嵌入式晶圆级球阵列(eWLB)。另外一种受欢迎的嵌入方式是将主动芯片嵌入多层线路板之间。多层板的嵌入技术包括Imbera的集成模块板(IMB)和AT&S的元件嵌入式封装(ECPR)。此外,多个研究项目和咨询机构对众多主动芯片嵌入式的相应技术和供应链问题进行了研究,这些项目和机构包括欧洲的芯片隐行项目,HERMES咨询,和Casio &CMK EWLP 咨询,它们共同的目标是开发低成本的芯片嵌入式技术,并将其工业化。

图1 芯片嵌入式结构(由Casio/CMK提供)

以往的芯片嵌入式技术有很多缺陷,如很多合格芯片会损耗在成品率差的基板层叠工序中,芯片嵌入工时较长,难于检测和返工等。但在近期的实践中,众多公司正在减少上述缺陷方面取得显著进步,并开发了支持日益成长的芯片嵌入需求的生产体系。将芯片嵌入工序移至线路板层叠工序的中流(mid-stream)可以帮助减少合格芯片的损耗。此外,利用成熟的,可大规模实施的薄膜层叠(thin film build-up)技术和多层板工艺,同时利用高效芯片粘贴和基于型板组装(panel-based assembly)的设备,可以帮助保障更坚实有效的工艺流程。这直接导致了市场转变,使芯片嵌入式技术更多地应用于2D和3D的封装结构中。

三、 市场转变

封装集成度的二维延伸已经到了一个转折点,先进的封装技术要求更高度的集成、减薄和成本效益。因此,芯片嵌入式的三维封装解决方案成为下一代产品中更具吸引力的集成手段。

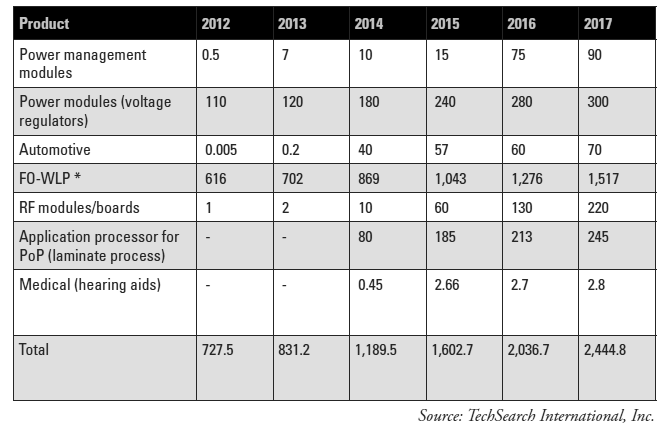

传统上,使用标准或先进的有机基板的多芯片粘贴方式局限于二维平面内,并用于多芯片模块(MCM)开发。而这种二维技术最先进的技术平台(2.5D TSV)由于高成本和不成熟的供应链而不能广泛应用。芯片嵌入式技术为在3D结构中集成异质芯片提供了一个有效的替换途径。由于成本效益高,它对消费类应用也颇具吸引力。事实上,集成芯片供应商(IDM)和芯片设计公司(fabless)都计划大规模发展芯片嵌入类产品,特别是在移动应用领域。图2是TechSearch 国际咨询对主动芯片嵌入类市场的预测[1]。

图2 芯片嵌入式市场预测 (每年百万颗)

注释:上述FO-WLP 包括基带、射频和电源管理芯片(主要是二维结构)

四、 芯片嵌入式平台

当前芯片嵌入式封装形式就像其应用那样多种多样。这不仅决定于制造方法的多样性,也决定于系统设计和考虑利益最大化的模块使用战略。

4.1 被动元件嵌入以减少噪声

芯片嵌入技术中被动(无源)元件嵌入的一个例子是将电容元件置于基板中。使电容靠近处理器芯片是减噪的一个有效方法。表面贴片的电容元件通常被置于芯片的3mm之外,以满足实施芯片虹吸下填料(capillary underfill)所需要的设计规则。而嵌入式的电容元件可以直接放在芯片下部,这不仅缩短了电感回路,也释放了基板表面宝贵的可用于表面贴片的面积。

4.2 主动芯片嵌入

通常,主动(有源)芯片嵌入可以减小封装高度。虽然可以用多种方法实施芯片嵌入,但最终的封装形式主要是以下三种类别之一:

1. 扇出型晶圆级封装

2. 在多层板中嵌入芯片

3. 模块型芯片嵌入

4.2.1 扇出型晶圆级封装 (FO-WLP)

在FO-WLP的生产中,第一步是将切割后的芯片置于晶圆持盘(carrier)中。这种工序叫做“芯片-先置”方法。在芯片放置之后,封装结构将在芯片周围形成,并重新形成塑封了的晶圆。“芯片-先置”的优势在于省略了芯片粘贴的回流步骤,因为扇出电路直接在芯片互联点焊盘上形成。这种流程的劣势是任何成品率的损失都是合格芯片的损耗。图3展示了一个FO-WLP封装。

图3 典型FO-WLP结构

4.2.2 在多层板中嵌入芯片

在多层板中嵌入芯片也是“芯片-先置”的流程。和FO-WLP流程类似,先将芯片粘贴在一个持盘中,然后封装结构在其周边构建。这种技术和FO-WLP技术的主要区别在于持盘模式是大块型板形式(panel format)而不局限于晶圆模式,同时它使用的嵌入介质是在基板生产中常用的材料(如,树脂材料,介电质,和增层材料)。ASE的zEASI技术和J-Device的WFOP(扇出型晶圆级封装)都是这种技术的表现。

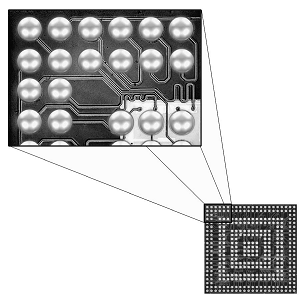

另外一种在多层板中嵌入芯片的方法是预先在基板上制造扇出结构单元,并检查出合格单元,然后只是在合格单元上进行芯片粘贴。这种被称作“芯片-中置”(Die-Mid)流程的主要优势在于减小了因扇出结构制造的良率而造成的成本提高。图4是“芯片-中置”流程而产生的多层板芯片嵌入的结构。

图4 在多层板中嵌入芯片 (Die-Mid 流程)

4.2.3 模块型芯片嵌入,“芯片-后置”(Die-Last)流程

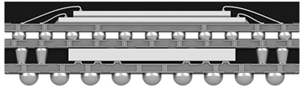

“Die-Mid”下一个逻辑上的进化是“芯片-后置”(Die-Last)流程,它是芯片嵌入更模块化的方法。在这个流程中,上端和下端的基板结构被预先制造,而芯片粘贴被放在整个流程的后端。这种方法的好处是芯片粘贴只发生在已知的合格的基板单元中,以减少合格芯片的损耗。特别是,当嵌入芯片的互联点增加或基板复杂度增加时,其优势更加明显。图5所示

为一个模块型芯片嵌入结构

图5 模块型芯片嵌入结构

4.3 封装叠加封装(PoP)

上述三种制造方法都可以支持封装叠加封装形式(PoP)。封装叠加的技术重点在于上部封装体和下部封装体之间的互联方式,以获得最大的互联密度。上下部封装体之间的互联可以是标准的JEDEC PoP 所定义的模式,或者是由客户定义的互联点扇入(Fan-In)模式。图6所示是扇入型PoP(Fan-In PoP)的例子。

图6 Fan-In PoP

4.4 封装尺寸减小

芯片嵌入技术可以减小封装厚度和整体封装尺寸,其原因主要在于:第一,使用无核基板。因为大多数的芯片嵌入扇出技术都使用一个暂时的持盘, 所以用有核基板没有必要。第二,层数减少。减小的线宽线距尺寸可以支持更高密度电路设计而无需基板层数增加。第三,更薄的芯片。嵌入式芯片与表面贴片相比可以得到更好冲击保护(如芯片碎裂)。因为嵌入的芯片更近于封装的中立点,所以热应力对它的破坏可以大大减小。因此,嵌入式封装支持薄型芯片使用。

4.5 真正的系统级封装

芯片嵌入技术正在驱动真正的系统级封装(SiP)的实现,使SiP发挥更大作用而不只是典型的多芯片模块。SiP技术的优势在于,它可以将不同技术组合在一起,从而在封装体内形成高度集成的系统,并充分优化封装体的成本、尺寸,和性能。这种集成通过减小电路长度、提高尺寸公差要求,和加强减噪来获得更高性能的产品。但是,高度系统集成也要求更综合的系统设计战略,这需要所涉及的价值链上的公司在更早的阶段开始合作,特别是同SiP封装厂商的合作。

对外包加工半导体封装测试(OSATs)供应商来说,高度系统集成导致了更多的封装形式,这要求封装更有灵活性、易于成本控制和有更高的组装成品率。为了平衡这些因素,解决方案之一是在型板状态下(at panel level)用“Die-Mid”制造流程进行芯片嵌入。Amkor Technology 正在开发这项技术。应用先进的基板制造工艺,这种芯片嵌入流程可灵活地用于制造各类专用电路互联,并具有高成品率的潜力。同时,多层板中的嵌入式芯片提供顶侧互联点,可以实现SiP异质芯片的集成。图7所示为一个集成嵌入式逻辑芯片和存储芯片的结构应用

图7 应用多层板嵌入式芯片的PoP(逻辑芯片和叠加的存储芯片)

五、 长期路线图

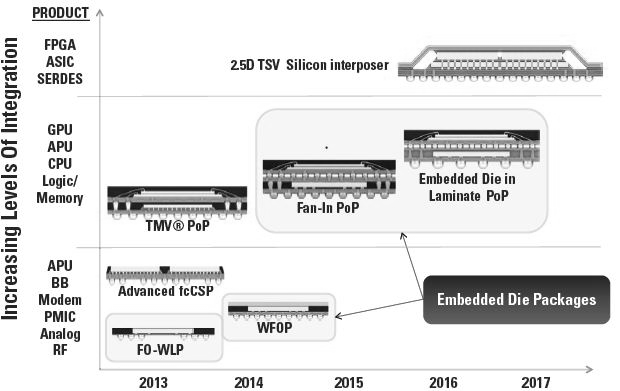

针对先进的移动应用,半导体工业不断对芯片封装技术提出更高的要求。异质集成正驱动封装技术进步以提供更薄型、更高性价比,和可升级的封装方式。图8展示了如何用芯片嵌入式封装技术来满足路线图的要求。

图8 先进封装集成路线图

如图8底部所示,FO-WLP和WFOP芯片嵌入技术可以很好地服务于二维应用(单芯片或多芯片模块结构)。应用举例包括应用处理器、基带处理器、电源管理芯片,和组合芯片。这些封装通常含有一层或两层的增层(build-up)电路,从成本和可靠性角度优化了这些二维嵌入技术。

如图8中部所示,多层板芯片嵌入技术是实现三维PoP应用的最好方式,如逻辑加存储集成结构。扇入型PoP和多层板芯片嵌入PoP可以在其芯片嵌入结构之上制造高密度互联阵列,从而可以用传统SMT(表面贴片技术)方法将另一个独立封装体组装于其上。常用的PoP结构是将应用处理芯片嵌入底部封装体中而将存储封装体置于上部。这种方式允许来自不同供应商的存储芯片的采购,从而简化供应链流程。

最后,图8上部标出2.5D TSV技术。它使用了带金属过孔的硅基板,目标市场是高端封装产品,如FPGAs, ASICs和需要高密度互联存储的产品。虽然2.5D TSV产品成本很高,但在无法用有机基板芯片嵌入技术实现的高密度系统集成设计中,却可能是最佳解决方案。

六、 结论

消费者对移动性、功能性和使用性的要求促成了移动装置、平板和网络市场的巨大增长。而这些又促成芯片功能的收敛和集成,并要求我们开发更为复杂和先进的封装技术。传统上,多芯片模块(MCMs)可以集成异质芯片,但MCMs只能局限于二维平面扩展。2.5D硅基板技术在三维空间提供了最高度集成,但其成本结构和供应链效益上还不够成熟,无法满足商业化要求。芯片嵌入技术在传统MCM和先进的2.5D 硅基板技术之间架起桥梁,可以为消费类应用提供高集成度,小型化,和较低成本的解决方案。令人兴奋的新的芯片嵌入结构,如WFOP, Fan-In PoP 和多层板嵌入增层PoP技术,正在为越来越多的移动通信装置中的模块化设计提供各类优化解决方案。

七、 感谢

衷心感谢全球半导体联合会(GSA,Global Semiconductor Alliance)允许我们以中文再次发表本文。本文原载于GSA Vol.21 No.1 Mar. 2014。

参考文献

[1] Carpenter, Karen, Linda Matthew, and E. Jan Varadaman,“Embedded Components: Why Now? Market, Applications, and Technologies”,Austin,TechSearch International, 2014

作者简介

Ron Huemoeller,Amkor先进封装技术开发部高级副总裁。Ron1995年加入Amkor,承担过各类高级管理职位。他目前负责Amkor企业战略、市场开发,和先进封装技术产品和技术平台的商业化。在加入Amkor之前,Ron是Cray Computer的工程部总监。Ron获Augsburg学院化学学士、Phoenix大学技术管理硕士,并获亚利桑那州立大学MBA。Amkor位于美国亚利桑那州。Ron.Huemoeller@amkor.com

Corey Reichman, Amkor先进封装技术开发部主任工程师。Corey于2005年加入Amkor,是Amkor FCMBGA封装技术的主要研发者。他目前的研发重点是Amkor的芯片嵌入式扇出解决方案,可用于高互联密度和特别薄的芯片封装应用。在加入Amkor之前,Corey在旧金山湾区的多家领先的软件技术公司中负责市场开发。Corey获亚利桑那州立大学市场学士,和技术硕士学位。Corey.Reichman@amkor.com

Curtis Zwenger,Amkor先进封装技术开发部高级总监。Curtis1999年加入Amkor,是Amkor小间距铜柱技术、穿塑孔技术(TMVR),和MEMS封装技术的主要研发者之一。他目前负责Amkor型板级扇出和芯片嵌入产品线的开发和商业化。加入Amkor之前,Curtis就职于摩托罗拉。他获科罗拉多州立大学机械工程学士和Phoenix大学MBA。Curtis.Zwenger@amkor.com

注释:ECPR是AT&S的注册商标;TMVR是Amkor Technology的注册商标。