摘要:系统集成是实现电子产品高性能,小型化和低成本目标的重要手段。与同芯片上的系统集成 (SoC)相比, 封装层次上的系统集成(SiP)的开发具有成本低、周期短和灵活性高等优势。本文以典型的无线电子系统为例,提出了有效的系统分割设计方法,介绍了一些用于子系统模块封装的方法,并强调了系统公司与封装、基板及其它主被动元件供应商之间协调合作对成功的模块式电子系统开发的重要性。

关键词:无线系统;系统型封装(SiP);小型化;铜柱技术;封装叠加 (PoP)

Abstract:System integration is a very important method to achieve performance improvement, miniaturization, and cost reduction in electronic product development. Compared with SoC solution, system level integration at packaging level may provide benefits that include more cost saving, more flexibility, and a shorter development cycle. In this paper, we have proposed a system design methodology to demonstrate that an effective wireless system design could be achieved when the right packaging solutions are adopted through collaboration and co-design among system, packaging, substrate, and other active/passive component companies.

Key Words:Wireless system; System-in-Package (SiP), Miniaturization; Module, Copper pillar; PoP

1 简介

线路板(PCB)的设计和制造对整个系统的开发制造成本和周期都有巨大影响[1]。平均来说,线路板的成本是整个电子产品成本的31%。在正在兴起的模块式PCB设计中,设计工程师将分散元件组成的线路板系统有效组合,变成由多个子系统组成的线路板系统,以期减少主板层数和面积,降低主板设计复杂度,缩短产品面世时间,简化供应链管理。

电子产品的开发应该平衡考虑系统里的主要因素,如性能,成本,尺寸,加工性,设计,灵活性,和供应链的管理 (图1),等等。无线通信系统通常有几个子系统组成, 如,典型的手机系统包括,基带,收发器,各式前端模块,存储器,供电管理,功放,天线,滤波器等。为了开发生产卓越而有竞争力的电子产品,系统集成越发重要。

和芯片上的系统集成 (SoC)相比,封装层次上的系统集成(SiP)在某些方面颇具优势,如降低系统成本、增加设计灵活性、缩短开发周期等[2]。当今无线通信技术领域正经历巨大变化,无论在芯片开发还是在封装技术上,小型化、高密度集成以及各类创新正成为主流,以应对产品增加功能、提高性能、降低成本、缩小体积和快速面世的挑战。芯片系统集成(SoC)和封装系统集成(SiP)必须相互补充,以获得最佳性能价格比去满足市场需要。

将整个射频/模拟/数字系统集成在一个芯片中非常困难,因为,系统通常还需要大量的存储器、双工器(duplexer)、过滤器、MEMS 元件、集成被动件和其它多媒体元件,等等。以创新的思路应对市场需求成为必然。三维封装因其高程度的立体和平面集成获得业界采纳。为了获得更好的设计灵活性和成本控制,系统设计者们也正在转向使用各类高端封装形式,如芯片叠加(stacked die),系统封装(SiP)模块,2.5D/3D 硅穿孔(TSV),封装叠加(PoP)等形式[3]。

图1 平衡的系统集成

如何根据其功能要求对整个系统进行合理分割,并使不同的子系统免于耦合,同时减少元件间的电磁波及噪声互扰,对设计开发模块式电子系统非常重要,需要有正确方法的指导。

在这篇文章里,我们针对典型的无线通信系统提出了有效的系统分割设计方法,介绍了一些用于子系统模块封装的方法,并强调了系统公司与封装、基板及其它主被动元件供应商之间协调合作对成功的模块式电子系统开发的重要性。具体包括:如何根据系统需求和其组合元件的功能对系统进行合理分割;如何应用各类封装技术以达到提高性能、小型化和降低成本的要求;设计系统封装模块需要考虑的问题,如成本优化、性能提升、运用已知合格芯片(known good die)重要性、设计可制造性、设计可测试性,以及设计的可重复使用性等。

2 无线系统及系统集成

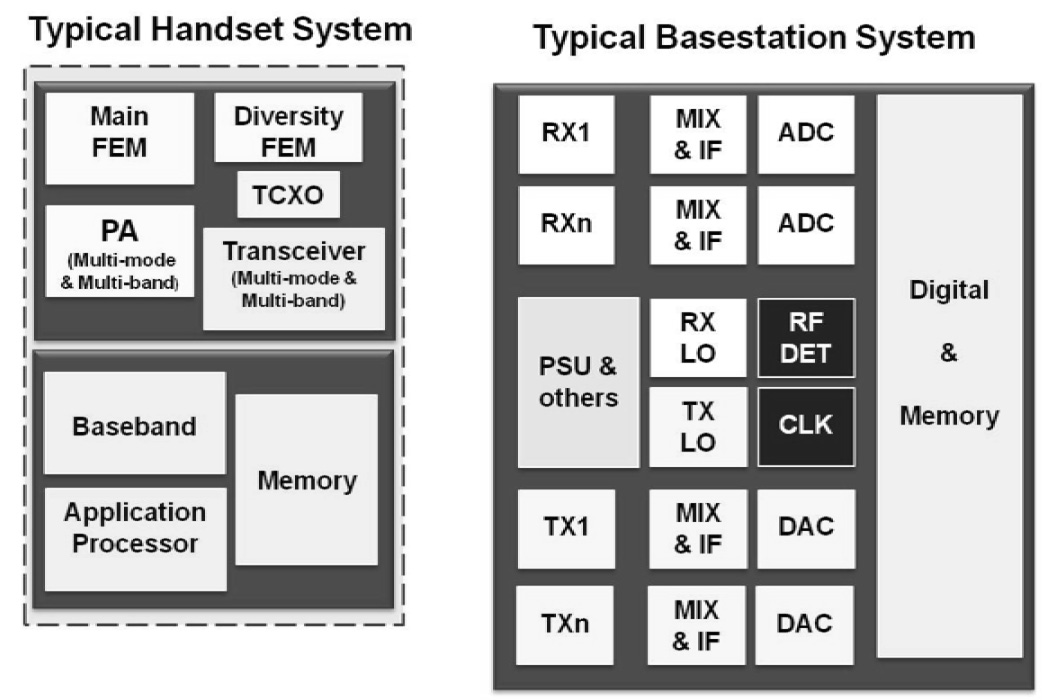

图2描述了无线系统中的手机系统和基站系统。在典型的OEM商务模式中,系统公司设计系统线路板,从芯片供应商处购买所需的分立器件,并使用电子制造商(EMS)的服务完成器件组装。这种商业模式决定了在产品尺寸和成本方面,系统公司之间很难形成较大差异。

当今手机市场竞争激烈,系统公司必须在增加功能、提高性能、降低成本、快速面市和小型化等方面做出更大努力。系统集成是必然的解决方案[4][5]。但只有优化集成才可以达到如图1所示的平衡状态。进行有效系统分割需要对系统有很好的理解,懂得独立器件的供应链情况,并知道用最佳的封装技术来完成模块系统封装。这通常依赖于系统公司、芯片供应公司和封装公司的密切合作。

图2 典型的无线系统: 手机和基站

芯片上的系统集成 (SoC)和封装层次上的系统(SiP)集成方法都是可行的,但它们必须相互补充以获取最佳系统性能价格比。

各类先进的封装技术,如封装叠加(PoP)、铜柱(copper pillar)、硅穿孔(TSV)、集成被动元件(IPD)、共形屏蔽(conformal shielding)、倒装塑封BGA(FCMBGA)等为系统集成提供了更多的可能性。

3 无线系统之分割

图3和图4分别描述了手机系统和基站系统的基本功能组合。

对整个系统进行全面透彻分析,并专注于产生有效子系统是非常重要的。一个或者多个子系统可以被封装成一个SiP模块,以达到提高性能、减少尺寸、节约成本和简化系统板设计的目的。

已知合格芯片(KGD)的供应和使用对成功的系统封装(SiP)开发和生产是十分关键的。KGD的合格率直接影响SiP生产中的良率。例如,在一个SiP中有8颗KGD,它们的良率都是99%,那么这个SiP在没有考虑其它因

图3 手机SiP系统集成

图4 基站收发系统